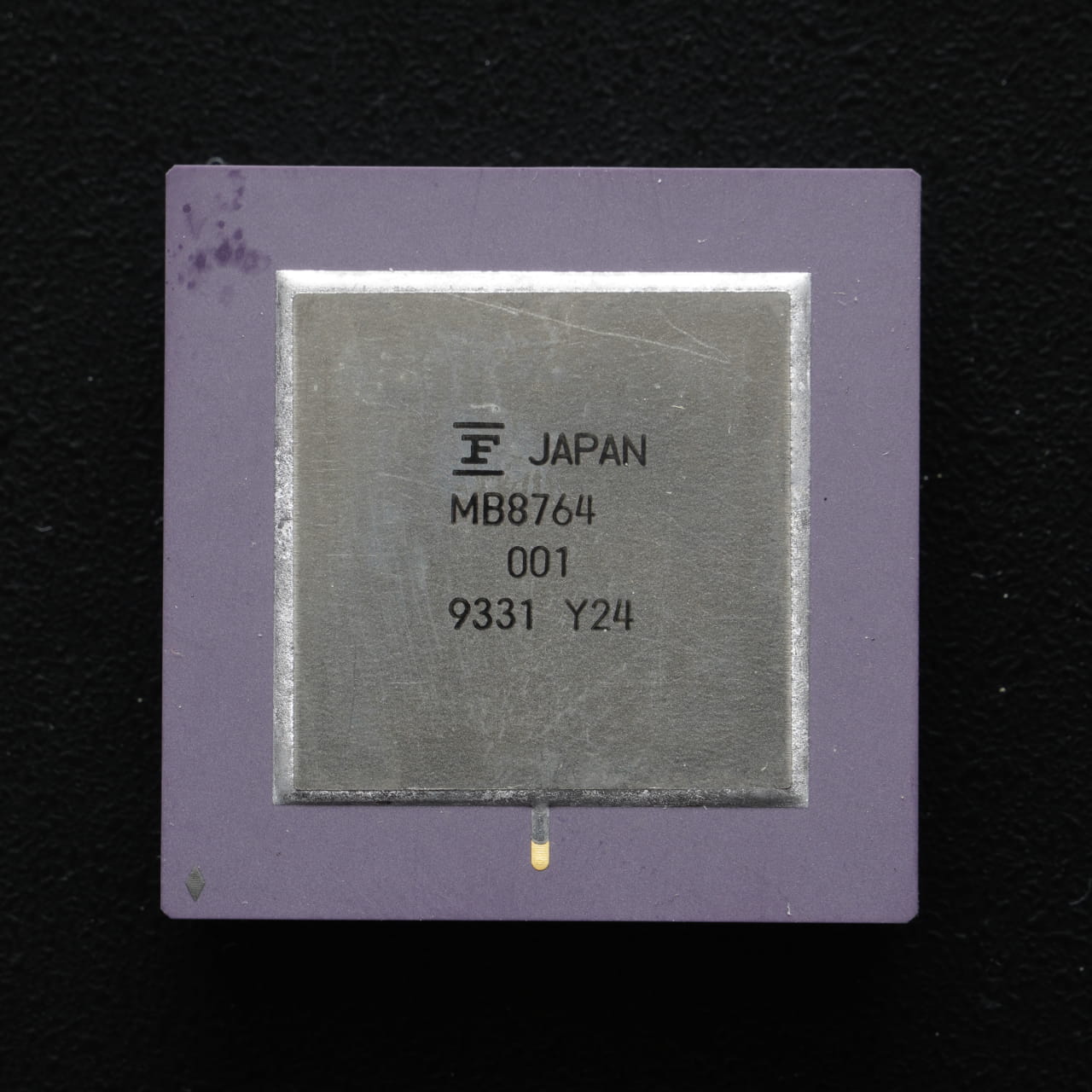

富士通 MB8764は、1983年に発表のCMOS Digital Signal Processor (DSP)だ [1]。 ゲート長2.3μm で91,000トランジスタを9.5×9.6 mm2に集積している [2]。 サイクルタイムは100 ns (10 MHz) で、16 bit × 16 bit → 26 bit の乗算器を持つ。 26 bit ÷ 16 bit → 16 bit の除算命令もある。 5Vで動作。

命令は24-bit wordで、内蔵ROM または外部ROM を利用可能。 データは16 bit word で、これも内蔵の128 word のメモリと外部接続のRAM が使える。 それぞれバスは分かれていて、命令用に10 ビット幅のアドレスバスと24 ビット幅のバス、 データ用には別の10 ビットのアドレスバスと16 ビットのバスが外に出されている。 命令用の内蔵ROM/外部ROMの切り替えは、サンプル回路を見た感じ、IRM をGND に落とすと外部ROM ということになるようだ。 内蔵ROM はマスクROM なので書き替えたりはできない。

レジスタはALU の左右に直結しているA, Bと、アキュムレータのD と各種フラグ、アドレス計算用のインデックスX, Y, スタックXS, XY, 加算レジスタAD1, AD2, virtual shift pointer VP, virtual shift mode register VSが主なものだ。

命令セットとしては、通常の命令に加え、乗算と加算を一命令で行なういわゆるfused multiply addがあるのがDSP らしさということになるだろうか。 制御レジスタCLP を使うことで飽和加算にもできる。便利。

乗算器のパイプライン動作と、I/O周りにかなり工夫が有りそうなのだが、詳細は確認でき次第情報を追加したい。

派生製品として、廉価版で外部メモリが使えないがDIPパッケージ入りのMB87064, マスクROMにADPCMのコーデックを書き込んだMB87067, MB87068がカタログに掲載されている。 周辺チップとして、μ-law/A-law からリニアPCM に変換する機能も付いたホストバスアダプタMB87069 もある。 アプリケーション回路として、スタンドアロンのエコーキャンセラーと、MC6800に接続する回路と、ADPCM コーデックが掲載されているので、このDSP は例えばサウンドカードとして使うとちょうど良い、というか作った人の意図通りということになるのだろう。 [2]のISSCCでの発表もSpeech recognitionという名前のセッションだ。

参考文献

- 8/16-bit microprocessors microcomputers peripherals 1987 data book. Fujitsu Limited and Fujitsu Microelectronics, Inc. OV0007-86ZF1. December 1986. [bitsavers.org]

- H. Kikuchi, T. Inaba, Y. Kubono, H. Hambe and T. Ikesawa, "A 23K gate CMOS DSP with 100ns multiplication," 1983 IEEE International Solid-State Circuits Conference. Digest of Technical Papers, New York, NY, USA, 1983, pp. 128-129, doi: 10.1109/ISSCC.1983.1156548.